在當今信息技術(shù)飛速發(fā)展的時代,集成電路(IC)作為電子設(shè)備的核心,其制造過程融合了物理、化學(xué)、材料科學(xué)和計算機科學(xué)的尖端成果。而將一顆復(fù)雜的芯片從設(shè)計圖紙變?yōu)楝F(xiàn)實中的硅片,不僅依賴于精密的制造工藝,更離不開可制造性設(shè)計(DFM)和專用軟件開發(fā)的協(xié)同支撐。這三者構(gòu)成了現(xiàn)代集成電路產(chǎn)業(yè)密不可分的三駕馬車,共同驅(qū)動著摩爾定律的延續(xù)與技術(shù)創(chuàng)新的步伐。

一、 集成電路制造工藝:從圖紙到硅片的精密雕刻

集成電路制造工藝,俗稱“制程”,是指將電路設(shè)計通過一系列復(fù)雜、精密的物理和化學(xué)步驟,在半導(dǎo)體晶圓上實現(xiàn)的過程。其主要流程包括:

- 晶圓制備:以高純度的單晶硅為原料,通過拉伸、切割、拋光等步驟,制備出表面近乎完美的晶圓。

- 薄膜沉積:在晶圓表面生長或沉積各種材料的薄膜,如二氧化硅(SiO?)、多晶硅、金屬等,作為后續(xù)加工的基底。

- 光刻:這是整個工藝的核心。利用光刻膠和特定波長的光源(如深紫外DUV、極紫外EUV),通過掩模版將電路圖案精確地“投影”到晶圓上。其分辨率直接決定了芯片上晶體管的最小尺寸(如7納米、5納米)。

- 刻蝕:將光刻后顯現(xiàn)出來的圖案,通過干法(等離子體)或濕法(化學(xué)溶液)刻蝕,轉(zhuǎn)移到下方的薄膜或硅基底上。

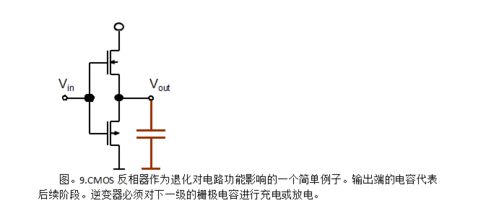

- 離子注入與擴散:向硅中注入特定的雜質(zhì)原子(摻雜),以形成晶體管所需的P區(qū)和N區(qū),從而構(gòu)建出MOSFET等核心器件。

- 化學(xué)機械拋光(CMP):平坦化晶圓表面,為后續(xù)添加新的金屬互聯(lián)層做好準備。

- 金屬化與互連:通過沉積和刻蝕形成多層金屬導(dǎo)線(通常為銅),將數(shù)以億計的晶體管連接起來,構(gòu)成完整的電路。

隨著工藝節(jié)點不斷微縮(進入納米尺度),制造過程面臨著物理極限、量子效應(yīng)、工藝變異等前所未有的挑戰(zhàn),這使得單純依靠工藝技術(shù)的進步變得愈發(fā)艱難。

二、 可制造性設(shè)計(DFM):連接設(shè)計與制造的橋梁

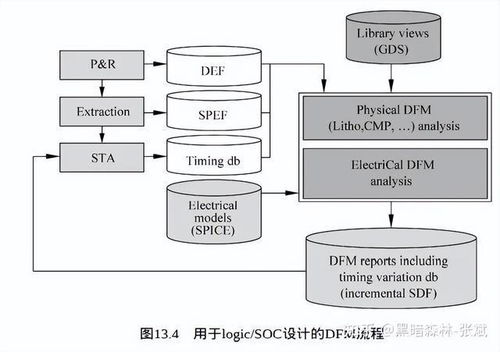

可制造性設(shè)計(Design for Manufacturability, DFM)正是在此背景下應(yīng)運而生并日益重要的理念與方法。它要求在芯片設(shè)計階段,就提前考慮和規(guī)避制造工藝中可能遇到的各種問題與限制,從而提高設(shè)計在現(xiàn)有工藝下的良率、可靠性和性能。DFM的核心目標是從“設(shè)計正確”走向“設(shè)計易于制造且高產(chǎn)”。其主要技術(shù)范疇包括:

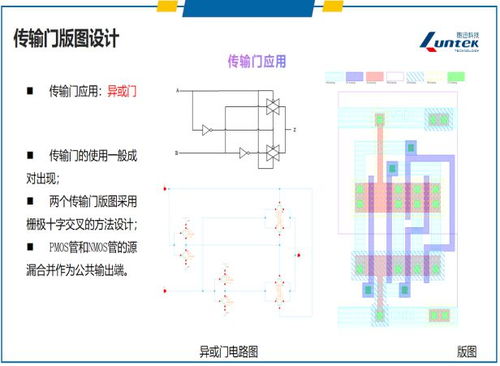

- 設(shè)計規(guī)則檢查(DRC)的演進:從簡單的幾何間距檢查,發(fā)展到包含復(fù)雜的光學(xué)鄰近效應(yīng)修正(OPC)規(guī)則、多重曝光規(guī)則等,確保設(shè)計圖形在經(jīng)過光刻等物理過程后仍能保持原貌。

- 工藝仿真與建模:建立精確的工藝模型(如光刻仿真、刻蝕仿真、CMP仿真),在設(shè)計階段預(yù)測制造后的實際形狀和電學(xué)參數(shù),識別潛在熱點(Hot Spot)。

- 良率導(dǎo)向設(shè)計(DFY):通過添加冗余結(jié)構(gòu)(如備用電路)、優(yōu)化布局以減少對工藝變異的敏感性、采用更穩(wěn)健的電路架構(gòu)等手段,主動提升芯片的預(yù)期良率。

- 統(tǒng)計時序分析:考慮到工藝參數(shù)(如晶體管閾值電壓、導(dǎo)線寬度)在晶圓內(nèi)和晶圓間的波動(工藝角),進行統(tǒng)計分析,確保芯片在所有變異情況下都能滿足時序要求。

DFM的本質(zhì)是讓設(shè)計與工藝實現(xiàn)“對話”,將制造知識前饋至設(shè)計端,從而減少試錯成本,加速產(chǎn)品上市時間。

三、 軟件開發(fā):賦能設(shè)計與制造的智能引擎

無論是復(fù)雜的芯片設(shè)計,還是精密的工藝控制與DFM實施,都離不開強大軟件工具的支撐。相關(guān)的軟件開發(fā)構(gòu)成了集成電路產(chǎn)業(yè)的“軟實力”基礎(chǔ)。

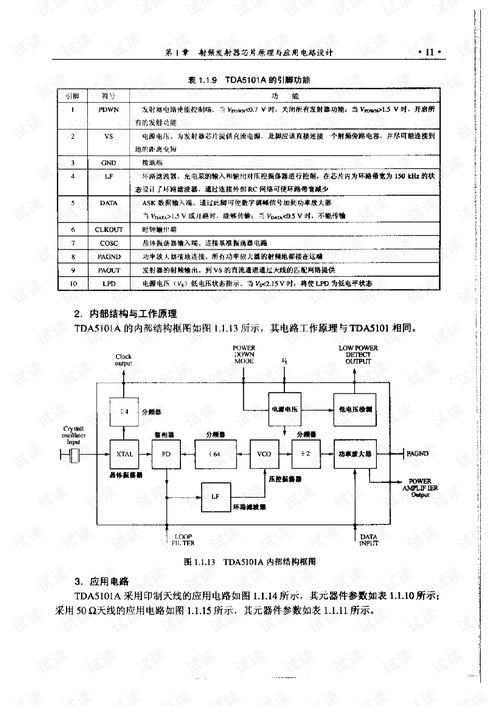

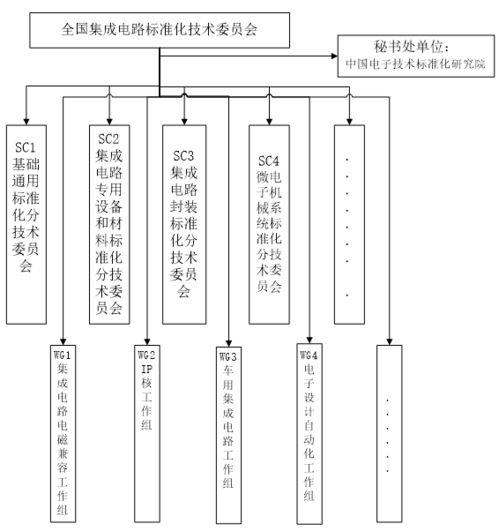

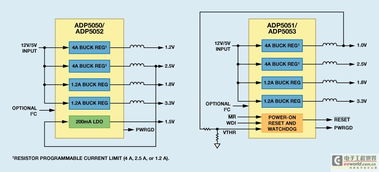

- 電子設(shè)計自動化(EDA)軟件:這是芯片設(shè)計的核心工具鏈,涵蓋了從系統(tǒng)架構(gòu)、邏輯綜合、電路仿真、物理布局布線到版圖驗證的全流程。EDA軟件集成了大量的DFM功能和工藝設(shè)計套件(PDK),是設(shè)計師將創(chuàng)意轉(zhuǎn)化為可制造版圖的關(guān)鍵平臺。

- 工藝仿真與計算光刻軟件:用于模擬光刻、刻蝕等物理過程,并生成用于OPC和反向光刻技術(shù)(ILT)的復(fù)雜掩模版圖形。隨著EUV光刻的應(yīng)用,相關(guān)軟件的算法復(fù)雜度和計算需求呈指數(shù)級增長。

- 制造執(zhí)行系統(tǒng)(MES)與良率管理系統(tǒng)(YMS):在晶圓廠中,軟件負責管理生產(chǎn)流程、跟蹤每一片晶圓的狀態(tài)、控制設(shè)備參數(shù)、收集海量生產(chǎn)數(shù)據(jù),并通過數(shù)據(jù)分析(常結(jié)合機器學(xué)習(xí))來診斷缺陷根源、持續(xù)優(yōu)化工藝、提升良率。

- TCAD(技術(shù)計算機輔助設(shè)計)軟件:用于模擬半導(dǎo)體器件的物理特性,幫助工藝工程師開發(fā)新的器件結(jié)構(gòu)和工藝模塊。

當前,人工智能與機器學(xué)習(xí)正在深度融入這些軟件工具中,用于更快的設(shè)計空間探索、更精準的工藝模型校準、更智能的缺陷分類和預(yù)測性維護,進一步推動產(chǎn)業(yè)向智能化方向發(fā)展。

結(jié)論

集成電路制造工藝、可制造性設(shè)計與軟件開發(fā)三者之間形成了緊密的閉環(huán)。先進的制造工藝為芯片性能提升提供了物理可能;可制造性設(shè)計確保了這種可能性能夠高效、穩(wěn)定地轉(zhuǎn)化為現(xiàn)實產(chǎn)品;而貫穿始終的軟件開發(fā)則為前兩者提供了實現(xiàn)、優(yōu)化和創(chuàng)新的智能工具與平臺。三者協(xié)同演進,共同應(yīng)對著后摩爾時代的技術(shù)挑戰(zhàn),不斷拓展集成電路技術(shù)的邊界,支撐起從智能手機、云計算到人工智能和自動駕駛的廣闊數(shù)字世界。